Computer Organization | Instruction Formats (Zero, One, Two and Three Address Instruction)

Last Updated :

29 Feb, 2024

In computer organization, instruction formats refer to the way instructions are encoded and represented in machine language. There are several types of instruction formats, including zero, one, two, and three-address instructions.

Each type of instruction format has its own advantages and disadvantages in terms of code size, execution time, and flexibility. Modern computer architectures typically use a combination of these formats to provide a balance between simplicity and power.

What are the Different Types of Instruction Fields?

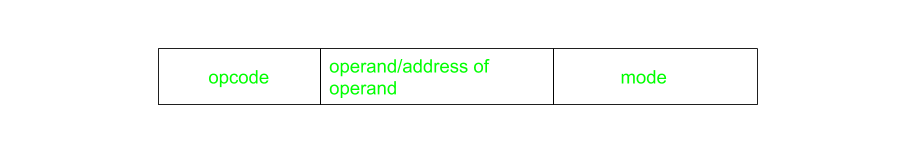

A computer performs a task based on the instructions provided. Instructions in computers are comprised of groups called fields. These fields contain different information for computers which are all written in 0s and 1s. Each field has a different significance or meaning, based on which a CPU decides what to perform. The most common fields are:

- The operation field specifies the operation to be performed, like addition.

- Address field which contains the location of the operand, i.e., register or memory location.

- Mode field which specifies how operand is to be founded.

An instruction is of variable length depending upon the number of addresses it contains. Generally, CPU organization is of three types based on the number of address fields:

- Single Accumulator organization

- General register organization

- Stack organization

In the first organization, the operation is performed using a special register called the accumulator. In the second, multiple registers are used for the computation purpose. In the third organization, the work on stack basis operation due to which it does not contain any address field. We generally see a blend of various organizations applied

Types of Instructions

Based on the number of addresses, instructions are classified as:

NOTE: We will use the X = (A+B)*(C+D) expression to showcase the procedure.

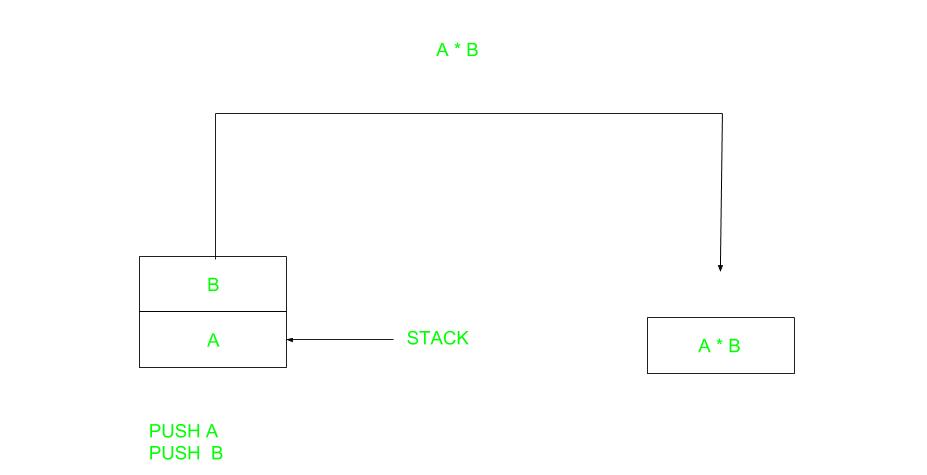

Zero Address Instructions

These instructions do not specify any operands or addresses. Instead, they operate on data stored in registers or memory locations implicitly defined by the instruction. For example, a zero-address instruction might simply add the contents of two registers together without specifying the register names.

Zero Address Instruction

A stack-based computer does not use the address field in the instruction. To evaluate an expression, it is first converted to reverse Polish Notation i.e. Postfix Notation.

Expression: X = (A+B)*(C+D)

Postfixed : X = AB+CD+*

TOP means top of stack

M[X] is any memory location

| PUSH |

A |

TOP = A |

| PUSH |

B |

TOP = B |

| ADD |

|

TOP = A+B |

| PUSH |

C |

TOP = C |

| PUSH |

D |

TOP = D |

| ADD |

|

TOP = C+D |

| MUL |

|

TOP = (C+D)*(A+B) |

| POP |

X |

M[X] = TOP |

One Address Instructions

These instructions specify one operand or address, which typically refers to a memory location or register. The instruction operates on the contents of that operand, and the result may be stored in the same or a different location. For example, a one-address instruction might load the contents of a memory location into a register.

This uses an implied ACCUMULATOR register for data manipulation. One operand is in the accumulator and the other is in the register or memory location. Implied means that the CPU already knows that one operand is in the accumulator so there is no need to specify it.

One Address Instruction

Expression: X = (A+B)*(C+D)

AC is accumulator

M[] is any memory location

M[T] is temporary location

| LOAD |

A |

AC = M[A] |

| ADD |

B |

AC = AC + M[B] |

| STORE |

T |

M[T] = AC |

| LOAD |

C |

AC = M[C] |

| ADD |

D |

AC = AC + M[D] |

| MUL |

T |

AC = AC * M[T] |

| STORE |

X |

M[X] = AC |

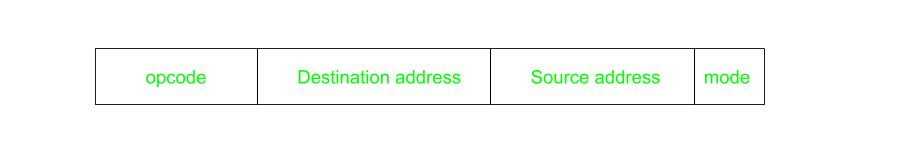

Two Address Instructions

These instructions specify two operands or addresses, which may be memory locations or registers. The instruction operates on the contents of both operands, and the result may be stored in the same or a different location. For example, a two-address instruction might add the contents of two registers together and store the result in one of the registers.

This is common in commercial computers. Here two addresses can be specified in the instruction. Unlike earlier in one address instruction, the result was stored in the accumulator, here the result can be stored at different locations rather than just accumulators, but require more number of bit to represent the address.

Two Address Instruction

Here destination address can also contain an operand.

Expression: X = (A+B)*(C+D)

R1, R2 are registers

M[] is any memory location

| MOV |

R1, A |

R1 = M[A] |

| ADD |

R1, B |

R1 = R1 + M[B] |

| MOV |

R2, C |

R2 = M[C] |

| ADD |

R2, D |

R2 = R2 + M[D] |

| MUL |

R1, R2 |

R1 = R1 * R2 |

| MOV |

X, R1 |

M[X] = R1 |

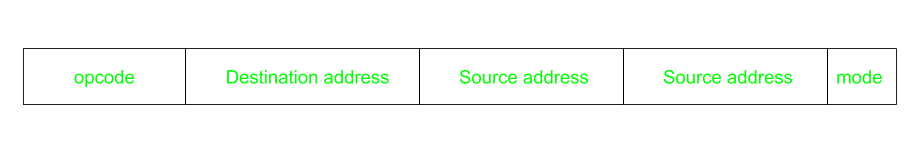

Three Address Instructions

These instructions specify three operands or addresses, which may be memory locations or registers. The instruction operates on the contents of all three operands, and the result may be stored in the same or a different location. For example, a three-address instruction might multiply the contents of two registers together and add the contents of a third register, storing the result in a fourth register.

This has three address fields to specify a register or a memory location. Programs created are much short in size but number of bits per instruction increases. These instructions make the creation of the program much easier but it does not mean that program will run much faster because now instructions only contain more information but each micro-operation (changing the content of the register, loading address in the address bus etc.) will be performed in one cycle only.

Three Address Instruction

Expression: X = (A+B)*(C+D)

R1, R2 are registers

M[] is any memory location

| ADD |

R1, A, B |

R1 = M[A] + M[B] |

| ADD |

R2, C, D |

R2 = M[C] + M[D] |

| MUL |

X, R1, R2 |

M[X] = R1 * R2 |

Advantages of Zero-Address, One-Address, Two-Address and Three-Address Instructions

Zero-address instructions

- They are simple and can be executed quickly since they do not require any operand fetching or addressing. They also take up less memory space.

One-address instructions

- They allow for a wide range of addressing modes, making them more flexible than zero-address instructions. They also require less memory space than two or three-address instructions.

Two-address instructions

- They allow for more complex operations and can be more efficient than one-address instructions since they allow for two operands to be processed in a single instruction. They also allow for a wide range of addressing modes.

Three-address instructions

- They allow for even more complex operations and can be more efficient than two-address instructions since they allow for three operands to be processed in a single instruction. They also allow for a wide range of addressing modes.

Disadvantages of Zero-Address, One-Address, Two-Address and Three-Address Instructions

Zero-address instructions

- They can be limited in their functionality and do not allow for much flexibility in terms of addressing modes or operand types.

One-address instructions

- They can be slower to execute since they require operand fetching and addressing.

Two-address instructions

- They require more memory space than one-address instructions and can be slower to execute since they require operand fetching and addressing.

Three-address instructions

- They require even more memory space than two-address instructions and can be slower to execute since they require operand fetching and addressing.

Overall, the choice of instruction format depends on the specific requirements of the computer architecture and the trade-offs between code size, execution time, and flexibility.

FAQs On Computer Organization Instruction Formats

1. Does Instruction Format affects Efficiency of Machines?

Answer:

Instruction Format has several impact on Instruction Execution, Memory Usage and Density of Code. It requires fewer mwmory access, that ultimately results in faster execution.

2. Does single architecture supports multiple Instruction Format?

Answer:

It is possiible for some architectures to allow multiple instruction format to run parallely. There can be variable length instruction encoding or different addressing modes.

Share your thoughts in the comments

Please Login to comment...