Microprocessor

Question 1

Which of the following addressing modes are suitable for program relocation at run time ?

(i) Absolute addressing (ii) Based addressing (iii) Relative addressing (iv) Indirect addressing

Question 2

Direction for questions 63 to 64:

Consider the following program segment for a hypothetical CPU having three user registers R1, R2 and R3.

Instruction Operation Instruction Size(in words) MOV R1,5000; R1 ¬ Memory[5000] 2 MOV R2, (R1); R2 ¬ Memory[(R1)] 1 ADD R2, R3; R2 ¬ R2 + R3 1 MOV 6000, R2; Memory [6000] ¬ R2 2 HALT Machine halts 1Consider that the memory is byte addressable with size 32 bits, and the program has been loaded starting from memory location 1000 (decimal). If an interrupt occurs while the CPU has been halted after executing the HALT instruction, the return address (in decimal) saved in the stack will be

Question 3

Directions for question 63 to 64: Consider the following program segment for a hypothetical CPU having three user registers R1, R2 and R3.

Instruction Operation Instruction Size(in words) MOV R1,5000; R1 ¬ Memory[5000] 2 MOV R2, (R1); R2 ¬ Memory[(R1)] 1 ADD R2, R3; R2 ¬ R2 + R3 1 MOV 6000, R2; Memory [6000] ¬ R2 2 HALT Machine halts 1

Let the clock cycles required for various operations be as follows: Register to/ from memory transfer: 3 clock cycles ADD with both operands in register : 1 clock cycle Instruction fetch and decode : 2 clock cycles per word The total number of clock cycles required to execute the program is

Question 4

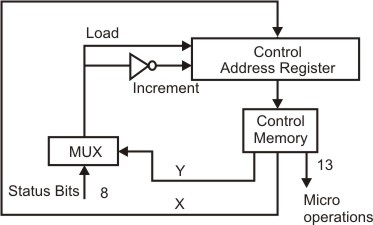

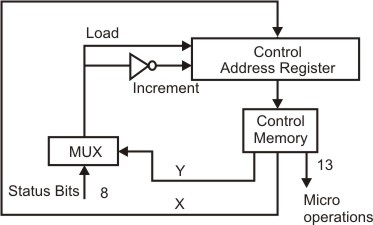

The microinstructions stored in the control memory of a processor have a width of 26 bits. Each microinstruction is divided into three fields: a micro-operation field of 13 bits, a next address field (X), and a MUX select field (Y). There are 8 status bits in the inputs of the MUX.

How many bits are there in the X and Y fields, and what is the size of the control memory in number of words?

How many bits are there in the X and Y fields, and what is the size of the control memory in number of words?

How many bits are there in the X and Y fields, and what is the size of the control memory in number of words?

How many bits are there in the X and Y fields, and what is the size of the control memory in number of words?Question 5

Consider the following assembly language program for a hypothetical processor. A, B, and C are 8 bit registers. The meanings of various instructions are shown as comments.

| MOV B, # 0 | ; | B ← 0 | |

| MOV C, # 8 | ; | C ← 8 | |

| Z : | CMP C, # 0 | ; | compare C with 0 |

| JZX | ; | jump to X if zero flag is set | |

| SUB C, # 1 | ; | C ← C - 1 | |

| RRC A, # 1 | ; | right rotate A through carry by one bit. Thus: | |

| ; | if the initial values of A and the carry flag are a7...a0 and | ||

| ; | c0 respectively, their values after the execution of this | ||

| ; | instruction will be c0a7...a1 and a0 respectively. | ||

| JC Y | ; | jump to Y if carry flag is set | |

| JMP Z | ; | jump to Z | |

| Y : | ADD B, # 1 | ; | B ← B + 1 |

| JMP Z | ; | jump to Z | |

| X : |

Question 6

Consider the following assembly language program for a hypothetical processor. A, B, and C are 8 bit registers. The meanings of various instructions are shown as comments.

Which of the following instructions when inserted at location X will ensure that the value of register A after program execution is the same as its initial value ?

| MOV B, # 0 | ; | B ← 0 | |

| MOV C, # 8 | ; | C ← 8 | |

| Z : | CMP C, # 0 | ; | compare C with 0 |

| JZX | ; | jump to X if zero flag is set | |

| SUB C, # 1 | ; | C ← C - 1 | |

| RRC A, # 1 | ; | right rotate A through carry by one bit. Thus: | |

| ; | if the initial values of A and the carry flag are a7...a0 and | ||

| ; | c0 respectively, their values after the execution of this | ||

| ; | instruction will be c0a7...a1 and a0 respectively. | ||

| JC Y | ; | jump to Y if carry flag is set | |

| JMP Z | ; | jump to Z | |

| Y : | ADD B, # 1 | ; | B ← B + 1 |

| JMP Z | ; | jump to Z | |

| X : |

Question 7

Question 10

What are the states of the Auxiliary Carry (AC) and Carry Flag (dCY) after executing the following 8085 program?

MVI L, 5DH MVI L, 6BH MOV A, H ADD L

There are 57 questions to complete.

Last Updated :

Take a part in the ongoing discussion