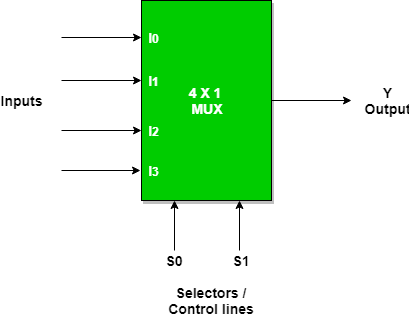

A multiplexer is a combinational circuit that has many data inputs and a single output, depending on control or select inputs. For N input lines, log2(N) selection lines are required, or equivalently, for 2^n input lines, n selection lines are needed. Multiplexers are also known as “N-to-1 selectors,” parallel-to-serial converters, many-to-one circuits, and universal logic circuits. They are mainly used to increase the amount of data that can be sent over a network within a certain amount of time and bandwidth.

Now the implementation of 4:1 Multiplexer using truth table and gates.

Multiplexer can act as universal combinational circuit. All the standard logic gates can be implemented with multiplexers.

a) Implementation of NOT gate using 2 : 1 Mux

NOT Gate :

We can analyze it

Y = x’.1 + x.0 = x’

It is NOT Gate using 2:1 MUX.

The implementation of NOT gate is done using “n” selection lines. It cannot be implemented using “n-1” selection lines. Only NOT gate cannot be implemented using “n-1” selection lines.

b) Implementation of AND gate using 2 : 1 Mux

AND GATE

This implementation is done using “n-1” selection lines.

c) Implementation of OR gate using 2 : 1 Mux using “n-1” selection lines.

OR GATE

Implementation of NAND, NOR, XOR and XNOR gates requires two 2:1 Mux. First multiplexer will act as NOT gate which will provide complemented input to the second multiplexer.

d) Implementation of NAND gate using 2 : 1 Mux

NAND GATE

e) Implementation of NOR gate using 2 : 1 Mux

NOR GATE

f) Implementation of EX-OR gate using 2 : 1 Mux

EX-OR GATE

g) Implementation of EX-NOR gate using 2 : 1 Mux

EX-NOR GATE

Implementation of Higher order MUX using lower order MUX

a) 4 : 1 MUX using 2 : 1 MUX

Three(3) ???? : 1 MUX are required to implement 4 : 1 MUX.

Similarly,

While 8 : 1 MUX require seven(7) ???? : 1 MUX, 16 : 1 MUX require fifteen(15) ???? :1 MUX, 64 : 1 MUX requires sixty three(63)​ 2 : 1 MUX.

Hence, we can draw a conclusion,

2n : 1 MUX requires (2^n – 1) 2 : 1 MUX.

b) 16 : 1 MUX using 4 : 1 MUX

In general, to implement B : 1 MUX using A : 1 MUX , one formula is used to implement the same.

B / A = K1,

K1/ A = K2,

K2/ A = K3

………………

KN-1 / A = KN = 1 (till we obtain 1 count of MUX).

And then add all the numbers of MUXes = K1 + K2 + K3 + …. + KN.

For example​ : To implement 64 : 1 MUX using 4 : 1 MUX

Using the above formula, we can obtain the same.

64 / 4 = 16

16 / 4 = 4

4 / 4 = 1 (till we obtain 1 count of MUX)

Hence, total number of 4 : 1 MUX are required to implement 64 : 1 MUX = 16 + 4 + 1 = 21.

An example to implement a boolean function if minimal and don’t care terms are given using MUX​.

f ( A, B, C) = ? ( 1, 2, 3, 5, 6 ) with don’t care (7) using 4 : 1 MUX using as

a) AB as select : ????xpanding the minterms to its boolean form and will see its 0 or 1 value in Cth place so that they can be placed in that manner.

b) AC as select : Expanding the minterms to its boolean form and will see its 0 or 1 value in Bth place so that they can be place in that manner.

c) BC as select : ????xpanding the minterms to its boolean form and will see its 0 or 1 value in Ath place so that they can be place in that manner.

Advantages and disadvantages of Multiplexers in Digital Logic:

Advantages of Multiplexers in Digital Logic:

1.Space-saving: Multiplexers consider numerous signs to be directed through a solitary channel, which recoveries space in computerized circuits.

2.Cost-successful: Multiplexers can assist with decreasing the expense of Advanced circuits by diminishing the quantity of parts required.

3.Time-saving: Multiplexers can save time in computerized circuits by decreasing the quantity of parts that should be wired together, subsequently diminishing the intricacy of the circuit.

4.Flexibility: Multiplexers are profoundly adaptable and can be utilized in a great many applications

Disadvantages of Multiplexers in Digital Logic:

1.Limited number of data sources: The quantity of sources of info that can be taken care of by a multiplexer is restricted by the quantity of control lines, which can be a disservice in certain applications.

2.Delay: Multiplexers can present some postpone in the sign way, which can influence the exhibition of the circuit.

3.Complex control rationale: The control rationale for multiplexers can be perplexing, particularly for bigger multiplexers with an enormous number of data sources.

4.Power utilization: Multiplexers can consume more power contrasted with other straightforward rationale entryways, particularly when they have countless data sources.

Share your thoughts in the comments

Please Login to comment...