Internal Registers of DMA Controller

Last Updated :

07 Mar, 2024

There are various types of controller

1. Base Address Register (16 bit)

2. Base Word Count Register (16 bit)

3. Current Address Register (16 bit)

4. Current Word Count Register (16 bit)

5. Temporary Address Register (16 bit)

6. Temporary Word Count Register (16 bit)

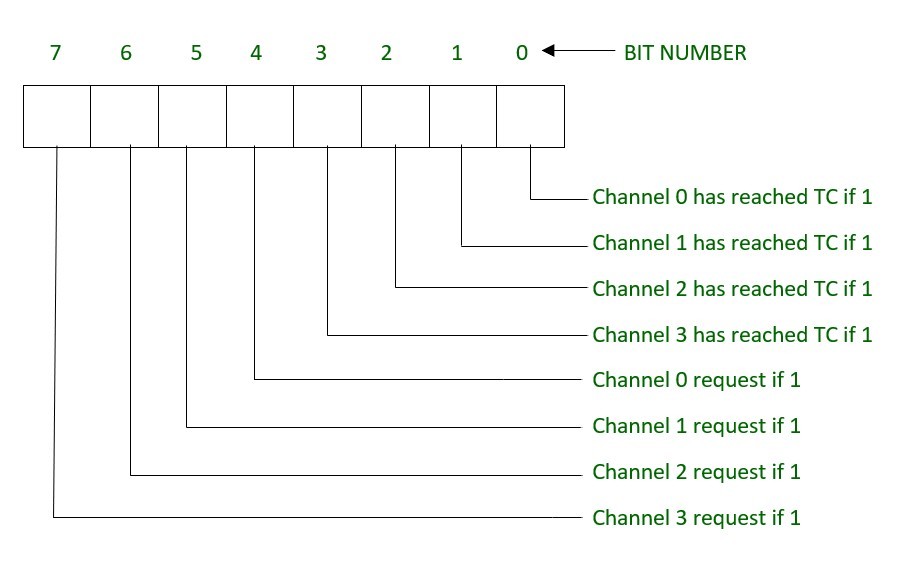

7. Status Register (8 bit)

8. Command Register (8 bit)

9. Temporary Register (8 bit)

10. Mode Register (8 bit)

11. Mask Register (4 bit)

12. Request Register (4 bit)

These are explained as following below.

- Base Address Register: It is a 16 bit register that stores the initial address from where the data transfer will take place in a DMA Controller. It is used to reload the Current Address Register after every operation.

- Base Word Count Register: It is a 16 bit register that stores the number of transfers to be performed during an operation. It is used to reload the Current Word Count Register after every operation.

- Current Address Register: It is a 16 bit register that stores the memory address for DMA data transfer. The value automatically increases or decreases after every operation based on how it is programmed. Each channel has its own Current Address Register.

- Current Word Count Register: It is a 16 bit register that stores the number of transfers remaining to be performed during an operation. The value automatically decreases after every operation.

- Temporary Address Register: It is a 16 bit register that stores the address of data during memory to memory transfer in a DMA Controller.

- Temporary Word Count Register: It is a 16 bit register that stores the number of transfers to be performed during a memory to memory transfer in a DMA Controller.

- Status Register: It is a 8 bit register that indicates which channel is currently under DMA services or which channels has reached its terminal count. It basically gives the status of the channels. The terminal counts(TC) bits indicates if the channel has reached its terminal count. If terminal count is reached, the transfers are terminated.

- Command Register: It is a 8 bit register that programs the DMA operation and initializes the channel to be used for data transfer.

- Temporary Register: It is a 8 bit register that holds data during memory to memory data transfer. It always contain the last byte transferred in previous memory to memory transfer operation.

- Mode Register: It is a 8 bit register that determines the operating mode, i.e., the transfer mode and other transfer parameters, for a channel. Each channel has its own mode register which is selected by bit positions 0 and 1.

- Mask Register: It is a 4 bit register that is used to mask a channel from requesting the DMA Services. When the mask on a channel is SET, the channel is disabled. It sets or clears all the mask on all the channels with just one command.

- Request Register: It is a 4 bit register that is used to request DMA data transfer by the software. It determines which channel is requesting for the data transfer.

Share your thoughts in the comments

Please Login to comment...