Half Adder Using Verilog

Last Updated :

16 Jul, 2023

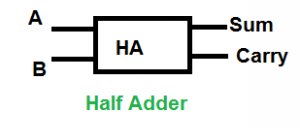

A half adder is a digital logic circuit that performs binary addition of two single-bit binary numbers. It has two inputs, A and B, and two outputs, SUM and CARRY. In this article we will discuss how to implement a Half adder Using Verilog HDL.

Aim: Develop a Half Adder using Verilog module.

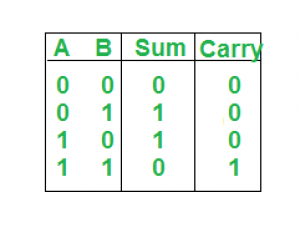

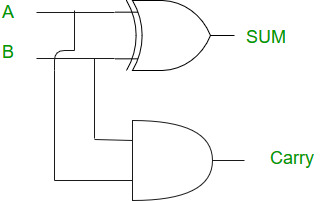

Theory: Half adder is also called as simple Binary Adder. It has two inputs A & B and outputs Sum & Carry.

- Sum is the XOR of inputs A&B

- Carry is the AND of inputs A&B

Truth Table

Truth Table

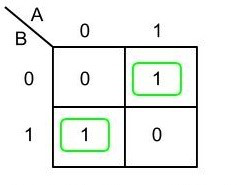

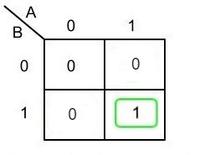

K-Map

S= A B' + A' B

S= A XOR B

Carry= A.B

Implementation Using Logic Gates

Verilog Code

Structural Method

module half_adder_structural (

input a, // Input 'a'

input b, // Input 'b'

output s, // Output 's' (Sum)

output c // Output 'c' (Carry)

);

xor gate_xor (s, a, b); // XOR gate for sum

and gate_and (c, a, b); // AND gate for carry

endmodule

Dataflow Representation

module half_adder_dataflow (

input a, // Input 'a'

input b, // Input 'b'

output s, // Output 's' (Sum)

output c // Output 'c' (Carry)

);

assign s = a ^ b; // Dataflow expression for sum

assign c = a & b; // Dataflow expression for carry

endmodule

Behavioral Representation

module half_adder_behavioral (

input a, // Input 'a'

input b, // Input 'b'

output s, // Output 's' (Sum)

output c // Output 'c' (Carry)

);

// Combinational logic equations for sum and carry

always @(*) begin

s = a ^ b; // XOR operation for sum

c = a & b; // AND operation for carry

end

endmodule

Test Bench

module half1_adder;

// Declare registers

reg d; // Register 'd' for input 'a'

reg e; // Register 'e' for input 'b'

// Declare wires

wire f; // Wire 'f' for output 's' (Sum)

wire g; // Wire 'g' for output 'c' (Carry)

// Instantiate half_adder module

half_adder half2_adder (.a(d), .b(e), .s(f), .c(g));

// Initial block for simulation

initial begin

$dumpvars(1, half1_adder); // Enable waveform dumping for simulation

// Test case 1

d = 1'b1; // Assign input 'a' as 1

$display("a=%b", d); // Display value of input 'a'

e = 1'b1; // Assign input 'b' as 1

$display("b=%b", e); // Display value of input 'b'

#10; // Wait for 10 time units

$display("s=%b", f); // Display value of output 's' (Sum)

$display("c=%b", g); // Display value of output 'c' (Carry)

// Test case 2

d = 1'b0; // Assign input 'a' as 0

$display("a=%b", d); // Display value of input 'a'

e = 1'b1; // Assign input 'b' as 1

$display("b=%b", e); // Display value of input 'b'

#10; // Wait for 10 time units

$display("s=%b", f); // Display value of output 's' (Sum)

$display("c=%b", g); // Display value of output 'c' (Carry)

// Test case 3

d = 1'b1; // Assign input 'a' as 1

$display("a=%b", d); // Display value of input 'a'

e = 1'b0; // Assign input 'b' as 0

$display("b=%b", e); // Display value of input 'b'

#10; // Wait for 10 time units

$display("s=%b", f); // Display value of output 's' (Sum)

$display("c=%b", g); // Display value of output 'c' (Carry)

// Test case 4

d = 1'b0; // Assign input 'a' as 0

$display("a=%b", d); // Display value of input 'a'

e = 1'b0; // Assign input 'b' as 0

$display("b=%b", e); // Display value of input 'b'

#10; // Wait for 10 time units

$display("s=%b", f); // Display value of output 's' (Sum)

$display("c=%b", g); // Display value of output 'c' (Carry)

end

endmodule

Share your thoughts in the comments

Please Login to comment...