Physical Memory Organisation of 8086

Last Updated :

28 Jan, 2024

Intel introduced its first 4-bit microprocessor in 1971 and 8-bit microprocessor in 8008 in 1972. However, this microprocessor could not survive due to its design and performance limitations. Later, the launch of the first 8-bit general purpose registers 8080 in 1974 by Intel is considered to be the first stepping stone towards the development of advanced microprocessors. The microprocessor 8085 was followed by 8080, with a few more added features to its architecture, which resulted in a functionally complete microprocessor.

Some Basic Terminologies in 8086 Physical Memory Organization

Below are some basic terminologies that are used in 8086 Physical Memory Organization

Memory Segment

It is a portion of memory that is used to address the data and instructions.

Offset Address

It is a part of the address that is added to the segment address to point to a specific location inside the segment.

For example: If the segment address is 1000H and offset address is 3000H then the memory location becomes 13000H( 10*1000H + 3000H)

Effective Address

It can be defined as the address of the data operand in the memory. It can be calculated from the formula

( Effective Address = Segment Register + Offset Address). In 8086 the segment registers are DS(Data segment), CS( code segment), ES( Extra Segment),SS (Stack segment).

Physical Address

It is defined as the actual address of the data or instruction where it is stored physically in the memory and calculated by (Physical Address = 10* segment Address + Offset Address).

Segmentation

It is a process of dividing the memory into segments and each segment can have a size of 64Kb( starting Address-0000H, last Address-FFFFH).

Brief Description About Physical Memory Organization

In 8086 one megabyte is physically organized as an odd bank and an even bank, each of 512Kbytes, addresses in parallel by a processor. Byte data with even address transferred on D7-D0 , while byte data with odd address is transferred on D15-D8 bus lines. To select an even or odd bank its has BHE and Ao as selector lines. Instruction stream is fetched from memory as words and is addressed internally by a processor. If it fetches a word from memory, the different possibilities are

- Both bytes may be data operands

- Both bytes may contain opcode

- One is opcode while other may be data

All these possibilities are taken care of by internal decoder circuit of microprocessor. This decoder detects the operand and data opcodes and derives the input for timing and control unit. The timing and control unit then derives signal required for execution of instruction. If the word is located in even address only one read or write cycle is required and if the word is located at odd address first read or write required for accessing lower byte while second one is required for accessing upper byte. Thus, two bus cycles are required if the word is located at an odd address.

8086 is a 16-Bit microprocessor and hence can access 2 bytes of data in one memory I/O read or write operation. But commercially available chips are only byte size i.e. they can store only one byte in memory location. To store 16-Bit data, two successive memory locations are used and lower byte of 16-Bit microprocessor is stored in first memory location while second byte is stored in next location. In 16-Bit read or write operation both of these bytes will read or write in single machine cycle. A map of 8086 memory system starts at 00000H and ends at FFFFFH. To achieve 16-Bit transfer using 8-Bit memory, in parallel map of system by the memory address will obviously be divided into memory bank as shown in the below figure.

Physical Memory Organization

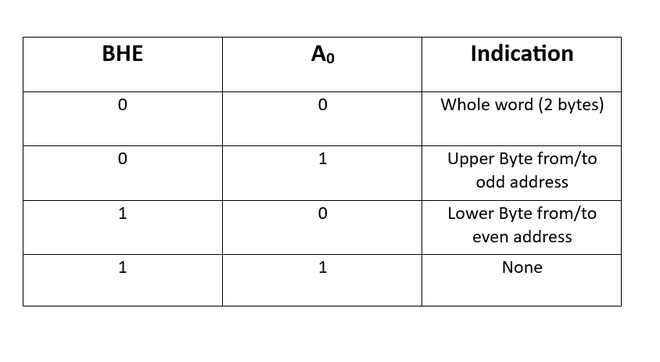

16-Bit data is stored at first address of map 00000H and it is to be transferred over D0-D7 of microprocessor which is in 8-bit memory. Higher byte of 16-bit data is stored in next address 00001H, it is to be transferred over D8-D15 of microprocessor bus. It is to be observed that all lower bytes are stored at even address and higher address are stored at odd address. If 8086 transfers a 16-bit data from/to memory both even and odd banks are selected for 16-bit operation. However, to maintain an upward compatibility with 8085, 8086 must able to implement 8-bit operation. Two signals Ao and BHE solve the problem of selection of appropriate memory banks as shown in the following figure.

Bus high enable and Ao

Certain locations are reserved for specific CPU operations. Locations FFFF0H-FFFFFH are reserved for operation including jump to initialization program. Locations 00000H-003FFH reserved for interrupt vector table. The interrupt structure provides space for a total of 256 interrupt vectors and these vectors need 4-bytes for storing it in the interrupt table. Hence 256 types of interrupt require 003FFH (1 Kbyte) locations for the complete interrupt vector table.

Following are the examples to calculate Physical Address:

1. The code segment(CS) is at 1000H and the destination index(DI) is at 4000H the physical address can be calculated by

PA = CS * 10 + DI +Displacement(if any)

CS = 1000H

DI = 4000H

Displacement = 0

PA = 1000H* 10 + 4000H + 0

PA = 14000H

2. The data segment is present at 3000H and source index is at 3000H then the physical address is

PA = DS * 10 + SI + Displacement( if any)

DS = 3000H

SI = 3000H

Displacement = 0

PA = 3000H * 10 + 3000H +0

PA = 33000H

FAQs on Physical Memory Organisation Of 8086

Q.1: What is the maximum memory capacity that 8086 processor can address?

Answer:

The 8086 microprocessor can address up to 1 MB(1024Kb) of data. Each memory location is uniquely identified by a 20-bit physical address.

Q.2: Are there any chances of segment overlap in Memory?

Answer:

Yes, two segments can be overlapped with each other, this allows to use the memory efficiently.

Q.3: How to calculate the physical address and effective address in memory?

Answer:

The displacement is not considered all the time but when relative addressing modes are used.

For effective Address: EA = Base Register+ index register(if any) + displacement(8/16 bit)

Q.4: What are the Addressing Modes of 8086?

Answer:

An addressing mode is the way of locating the data in the memory. Addressing modes are classified as Sequential control transfer instructions and Branch control instruction.

Q.5: Mention some of the Advantages of memory segmentation?

Answer:

- By memory segmentation we can achieve protection of data, code and stack data.

- program relocation is possible(Ability to run the same program in different memory location without changing its offset address).

- By Segmentation the system speed can be improved so the processor can easily perform data retrieve operation on memory.

Share your thoughts in the comments

Please Login to comment...