Pipelining and Addressing modes

Question 31

Question 32

X: Indirect addressing 1 : Loops Y: Immediate addressing 2 : Pointers Z: Auto decrement addressing 3: Constantsis

Question 33

S1: A memory operand S2: A processor register S3: An implied accumulator register

Question 34

Question 35

• Store the current value of PC in the stack. • Store the value of PSW register in the stack. • Load the starting address of the subroutine in PC.The content of PC just before the fetch of a CALL instruction is (5FA0)16. After execution of the CALL instruction, the value of the stack pointer is

A.(016A)16

B.(016C)16

C.(0170)16

D.(0172)16

Question 36

Consider the sequence of machine instructions given below:

MUL R5, R0, R1 DIV R6, R2, R3 ADD R7, R5, R6 SUB R8, R7, R4

In the above sequence, R0 to R8 are general purpose registers. In the instructions shown, the first register stores the result of the operation performed on the second and the third registers. This sequence of instructions is to be executed in a pipelined instruction processor with the following 4 stages: (1) Instruction Fetch and Decode (IF), (2) Operand Fetch (OF), (3) Perform Operation (PO) and (4) Write back the Result (WB). The IF, OF and WB stages take 1 clock cycle each for any instruction. The PO stage takes 1 clock cycle for ADD or SUB instruction, 3 clock cycles for MUL instruction and 5 clock cycles for DIV instruction. The pipelined processor uses operand forwarding from the PO stage to the OF stage. The number of clock cycles taken for the execution of the above sequence of instructions is ___________

Question 37

OP Ri, Rj, Rk

where operation OP is performed on contents of registers Rj and Rk and the result is stored in register Ri. I1 : ADD R1, R2, R3 I2 : MUL R7, R1, R3 I3 : SUB R4, R1, R5 I4 : ADD R3, R2, R4 I5 : MUL R7, R8, R9Consider the following three statements:

S1: There is an anti-dependence between instructions I2 and I5.

S2: There is an anti-dependence between instructions I2 and I4.

S3: Within an instruction pipeline an anti-dependence always

creates one or more stalls.

Which one of above statements is/are correct?

Question 38

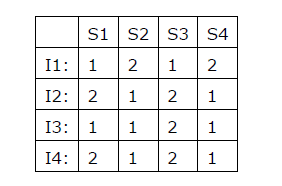

Time -->

-----------------------------

1 2 3 4 5

-----------------------------

S1 | X | | | | X |

S2 | | X | | X | |

S3 | | | X | | |

The minimum average latency (MAL) is __________

Question 39

Question 40

There are 94 questions to complete.