GATE-CS-2004

Question 51

A and B are the only two stations on an Ethernet. Each has a steady queue of frames to send. Both A and B attempt to transmit a frame, collide, and A wins the first backoff race. At the end of this successful transmission by A, both A and B attempt to transmit and collide. The probability that A wins the second backoff race is:

Question 52

The routing table of a router is shown below:

Destination Sub net mask Interface 128.75.43.0 255.255.255.0 Eth0 128.75.43.0 255.255.255.128 Eth1 192.12.17.5 255.255.255.255 Eth3 default Eth2On which interfaces will the router forward packets addressed to destinations 128.75.43.16 and 192.12.17.10 respectively?

Question 53

Consider three IP networks A, B and C. Host HA in network A sends messages each containing 180 bytes of application data to a host HC in network C. The TCP layer prefixes a 20 byte header to the message. This passes through an intermediate network B. The maximum packet size, including 20 byte IP header, in each network is

A : 1000 bytes

B : 100 bytes

C : 1000 bytes

The network A and B are connected through a 1 Mbps link, while B and C are connected by a 512 Kbps link (bps = bits per second).

Assuming that the packets are correctly delivered, how many bytes, including headers, are delivered to the IP layer at the destination for one application message, in the best case ? Consider only data packets.

Assuming that the packets are correctly delivered, how many bytes, including headers, are delivered to the IP layer at the destination for one application message, in the best case ? Consider only data packets.

Assuming that the packets are correctly delivered, how many bytes, including headers, are delivered to the IP layer at the destination for one application message, in the best case ? Consider only data packets.

Assuming that the packets are correctly delivered, how many bytes, including headers, are delivered to the IP layer at the destination for one application message, in the best case ? Consider only data packets.Question 54

Consider three IP networks A, B and C. Host HA in network A sends messages each containing 180 bytes of application data to a host HC in network C. The TCP layer prefixes a 20 byte header to the message. This passes through an intermediate network B. The maximum packet size, including 20 byte IP header, in each network is

A : 1000 bytes

B : 100 bytes

C : 1000 bytes

The network A and B are connected through a 1 Mbps link, while B and C are connected by a 512 Kbps link (bps = bits per second).

What is the rate at which application data is transferred to host HC? Ignore errors, acknowledgements, and other overheads.

What is the rate at which application data is transferred to host HC? Ignore errors, acknowledgements, and other overheads.

What is the rate at which application data is transferred to host HC? Ignore errors, acknowledgements, and other overheads.

What is the rate at which application data is transferred to host HC? Ignore errors, acknowledgements, and other overheads.Question 55

A circuit outputs a digit in the form of 4 bits. 0 is represented by 0000, 1 by 0001, ..., 9 by 1001. A combinational circuit is to be designed which takes these 4 bits as input and outputs 1 if the digit ≥ 5, and 0 otherwise. If only AND, OR and NOT gates may be used, what is the minimum number of gates required?

Question 56

Which are the essential prime implicants of the following Boolean function?

f(a, b, c) = a\'c + ac\' + b\'c

Question 57

Consider a multiplexer with X and Y as data inputs and Z as control input. Z = 0 selects input X, and Z = 1 selects input Y. What are the connections required to realize the 2-variable Boolean function f = T + R, without using any additional hardware ?

Question 58

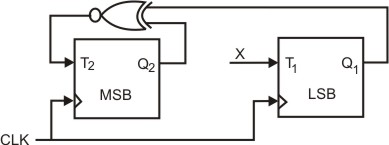

Consider the partial implementation of a 2-bit counter using T flip-flops following the sequence 0-2-3-1-0, as shown below

[/caption]

[/caption]

To complete the circuit, the input X should be

Question 59

A 4-bit carry lookahead adder, which adds two 4-bit numbers, is designed using AND, OR, NOT, NAND, NOR gates only. Assuming that all the inputs are available in both complemented and uncomplemented forms and the delay of each gate is one time unit, what is the overall propagation delay of the adder? Assume that the carry network has been implemented using two-level AND-OR logic.

Question 60

Direction for questions 63 to 64:

Consider the following program segment for a hypothetical CPU having three user registers R1, R2 and R3.

Instruction Operation Instruction Size(in words) MOV R1,5000; R1 ¬ Memory[5000] 2 MOV R2, (R1); R2 ¬ Memory[(R1)] 1 ADD R2, R3; R2 ¬ R2 + R3 1 MOV 6000, R2; Memory [6000] ¬ R2 2 HALT Machine halts 1Consider that the memory is byte addressable with size 32 bits, and the program has been loaded starting from memory location 1000 (decimal). If an interrupt occurs while the CPU has been halted after executing the HALT instruction, the return address (in decimal) saved in the stack will be

There are 90 questions to complete.

Last Updated :

Take a part in the ongoing discussion