Combinational Circuits

Question 1

A multiplexer is placed between a group of 32 registers and an accumulator to regulate data movement such that at any given point in time the content of only one register will move to the accumulator. The number of select lines needed for the multiplexer is _________ .

Note - This question was Numerical Type.

Question 2

If there are m input lines n output lines for a decoder that is used to uniquely address a byte addressable 1 KB RAM, then the minimum value of m+n is ________ .

Note - This question was Numerical Type.

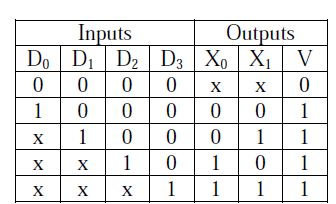

Question 3

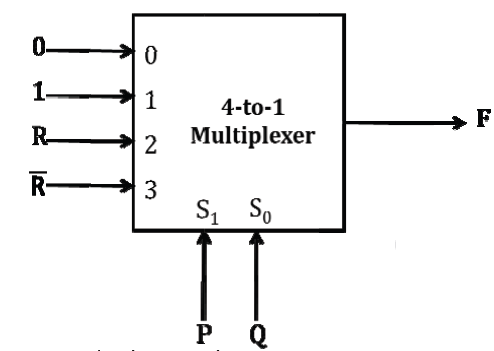

Question 4

Question 5

How many 3-to-8 line decoders with an enable input are needed to construct a 6-to-64 line decoder without using any other logic gates?

Question 6

Suppose only one multiplexer and one inverter are allowed to be used to implement any Boolean function of n variables. What is the minimum size of the multiplexer needed?

Question 7

In a look-ahead carry generator, the carry generate function Gi and the carry propagate function Pi for inputs Ai and Bi are given by:

Pi = Ai ⨁ Bi and Gi = AiBiThe expressions for the sum bit Si and the carry bit Ci+1 of the look-ahead carry adder are given by:

Si = Pi ⨁ Ci and Ci+1 = Gi + PiCi , where C0 is the input carry.Consider a two-level logic implementation of the look-ahead carry generator. Assume that all Pi and Gi are available for the carry generator circuit and that the AND and OR gates can have any number of inputs. The number of AND gates and OR gates needed to implement the look-ahead carry generator for a 4-bit adder with S3, S2, S1, S0 and C4 as its outputs are respectively:

Question 8

Question 9

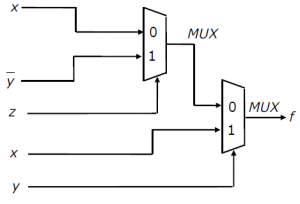

Consider the following combinational function block involving four Boolean variables x, y, a, b where x, a, b are inputs and y is the output.

C

Which one of the following digital logic blocks is the most suitable for implementing this function?

f (x, y, a, b)

{

if (x is 1) y = a;

else y = b;

}

Question 10

There are 55 questions to complete.

Last Updated :

Take a part in the ongoing discussion