GATE-CS-2005

Question 61

Consider line number 3 of the following C- program.

int main ( ) { /* Line 1 */

int I, N; /* Line 2 */

fro (I = 0, I < N, I++); /* Line 3 */

}

Identify the compiler\'s response about this line while creating the object-module

Question 62

Question 63

Question 64

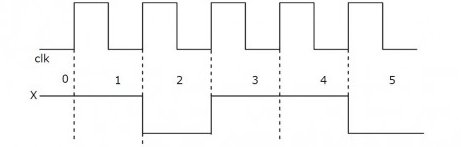

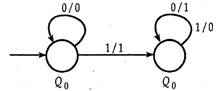

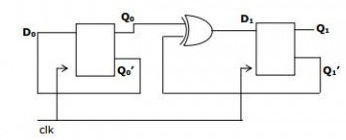

Consider the following circuit.

The flip-flops are positive edge triggered D FFs. Each state is designated as a two bit string Q0Q1. Let the initial state be 00. The state transition sequence is:

A) B) C) D)

Question 65

Consider a three word machine instruction

ADD A[R0], @ BThe first operand (destination) "A [R0]" uses indexed addressing mode with R0 as the index register. The second operand (source) "@ B" uses indirect addressing mode. A and B are memory addresses residing at the second and the third words, respectively. The first word of the instruction specifies the opcode, the index register designation and the source and destination addressing modes. During execution of ADD instruction, the two operands are added and stored in the destination (first operand). The number of memory cycles needed during the execution cycle of the instruction is

Question 66

Match each of the high level language statements given on the left hand side with the most natural addressing mode from those listed on the right hand side.

1 A[1] = B[J]; a Indirect addressing 2 while [*A++]; b Indexed, addressing 3 int temp = *x; c Autoincrement

Question 67

Consider a direct mapped cache of size 32 KB with block size 32 bytes. The CPU generates 32 bit addresses. The number of bits needed for cache indexing and the number of tag bits are respectively

Question 68

A 5 stage pipelined CPU has the following sequence of stages:

IF — Instruction fetch from instruction memory,

RD — Instruction decode and register read,

EX — Execute: ALU operation for data and address computation,

MA — Data memory access - for write access, the register read

at RD stage is used,

WB — Register write back.

Consider the following sequence of instructions:

I1 : L R0, 1oc1; R0 <= M[1oc1]

I2 : A R0, R0; R0 <= R0 + R0

I3 : S R2, R0; R2 <= R2 - R0

Let each stage take one clock cycle.

What is the number of clock cycles taken to complete the above sequence of instructions starting from the fetch of I1 ?

Question 69

A device with data transfer rate 10 KB/sec is connected to a CPU. Data is transferred byte-wise. Let the interrupt overhead be 4 microsec. The byte transfer time between the device interface register and CPU or memory is negligible. What is the minimum performance gain of operating the device under interrupt mode over operating it under program controlled mode?

Question 70

Consider a disk drive with the following specifications:

16 surfaces, 512 tracks/surface, 512 sectors/track, 1 KB/sector, rotation speed 3000 rpm. The disk is operated in cycle stealing mode whereby whenever one byte word is ready it is sent to memory; similarly, for writing, the disk interface reads a 4 byte word from the memory in each DMA cycle. Memory cycle time is 40 nsec. The maximum percentage of time that the CPU gets blocked during DMA operation is:

There are 90 questions to complete.

Last Updated :

Take a part in the ongoing discussion