GATE-CS-2004

Question 61

Directions for question 63 to 64: Consider the following program segment for a hypothetical CPU having three user registers R1, R2 and R3.

Instruction Operation Instruction Size(in words) MOV R1,5000; R1 ¬ Memory[5000] 2 MOV R2, (R1); R2 ¬ Memory[(R1)] 1 ADD R2, R3; R2 ¬ R2 + R3 1 MOV 6000, R2; Memory [6000] ¬ R2 2 HALT Machine halts 1

Let the clock cycles required for various operations be as follows: Register to/ from memory transfer: 3 clock cycles ADD with both operands in register : 1 clock cycle Instruction fetch and decode : 2 clock cycles per word The total number of clock cycles required to execute the program is

Question 62

Question 63

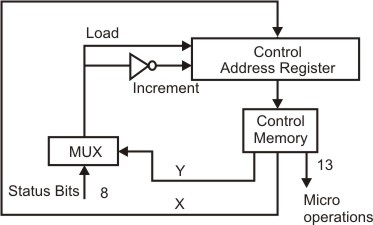

How many bits are there in the X and Y fields, and what is the size of the control memory in number of words?

How many bits are there in the X and Y fields, and what is the size of the control memory in number of words?Question 64

Question 65

Question 66

Question 68

How many solutions does the following system of linear equations have ?

-x + 5y = -1 x - y = 2 x + 3y = 3

Question 69

The following is the incomplete operation table a 4-element group.

* e a b c e e a b c a a b c e b c

The last row of the table is

Question 70

The inclusion of which of the following sets into

S = {{1, 2}, {1, 2, 3}, {1, 3, 5}, (1, 2, 4), (1, 2, 3, 4, 5}}

is necessary and sufficient to make S a complete lattice under the partial order defined by set containment ?

There are 90 questions to complete.