Pipelining and Addressing modes

Question 21

P1: Four-stage pipeline with stage

latencies 1 ns, 2 ns, 2 ns, 1 ns.

P2: Four-stage pipeline with stage

latencies 1 ns, 1.5 ns, 1.5 ns, 1.5 ns.

P3: Five-stage pipeline with stage

latencies 0.5 ns, 1 ns, 1 ns, 0.6 ns, 1 ns.

P4: Five-stage pipeline with stage

latencies 0.5 ns, 0.5 ns, 1 ns, 1 ns, 1.1 ns.

Which processor has the highest peak clock frequency?

Question 22

Question 23

Question 24

ADD A[R0], @ BThe first operand (destination) "A [R0]" uses indexed addressing mode with R0 as the index register. The second operand (source) "@ B" uses indirect addressing mode. A and B are memory addresses residing at the second and the third words, respectively. The first word of the instruction specifies the opcode, the index register designation and the source and destination addressing modes. During execution of ADD instruction, the two operands are added and stored in the destination (first operand). The number of memory cycles needed during the execution cycle of the instruction is

Question 25

1 A[1] = B[J]; a Indirect addressing 2 while [*A++]; b Indexed, addressing 3 int temp = *x; c Autoincrement

Question 26

A 5 stage pipelined CPU has the following sequence of stages:

IF — Instruction fetch from instruction memory,

RD — Instruction decode and register read,

EX — Execute: ALU operation for data and address computation,

MA — Data memory access - for write access, the register read

at RD stage is used,

WB — Register write back.

Consider the following sequence of instructions:

I1 : L R0, 1oc1; R0 <= M[1oc1]

I2 : A R0, R0; R0 <= R0 + R0

I3 : S R2, R0; R2 <= R2 - R0

Let each stage take one clock cycle.

What is the number of clock cycles taken to complete the above sequence of instructions starting from the fetch of I1 ?

Question 27

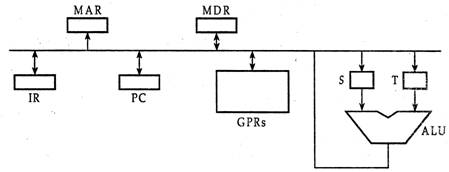

Consider the following data path of a CPU.

The, ALU, the bus and all the registers in the data path are of identical size. All operations including incrementation of the PC and the GPRs are to be carried out in the ALU. Two clock cycles are needed for memory read operation - the first one for loading address in the MAR and the next one for loading data from the memory bus into the MDR 79.

The instruction “call Rn, sub” is a two word instruction. Assuming that PC is incremented during the fetch cycle of the first word of the instruction, its register transfer interpretation is

Rn < = PC + 1; PC < = M[PC];

The minimum number of clock cycles needed for execution cycle of this instruction is.

Question 28

Question 29

1. The j + 1-st instruction uses the result of the j-th instruction

as an operand

2. The execution of a conditional jump instruction

3. The j-th and j + 1-st instructions require the ALU at the same

time

Which of the above can cause a hazard ?

There are 94 questions to complete.