Number Representation

Question 41

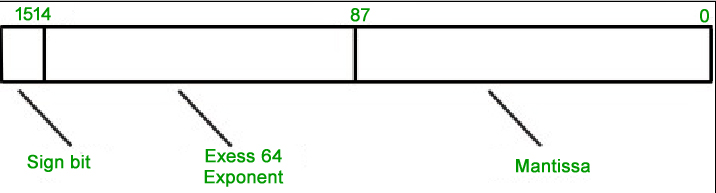

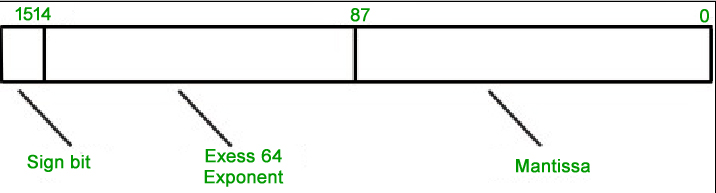

Consider the following floating point format

Mantissa is a pure fraction in sign-magnitude form. The normalized representation for the above format is specified as follows. The mantissa has an implicit 1 preceding the binary (radix) point. Assume that only 0\'s are padded in while shifting a field. The normalized representation of the above number (0.239 × 213) is:

Mantissa is a pure fraction in sign-magnitude form. The normalized representation for the above format is specified as follows. The mantissa has an implicit 1 preceding the binary (radix) point. Assume that only 0\'s are padded in while shifting a field. The normalized representation of the above number (0.239 × 213) is:

Mantissa is a pure fraction in sign-magnitude form. The normalized representation for the above format is specified as follows. The mantissa has an implicit 1 preceding the binary (radix) point. Assume that only 0\'s are padded in while shifting a field. The normalized representation of the above number (0.239 × 213) is:

Mantissa is a pure fraction in sign-magnitude form. The normalized representation for the above format is specified as follows. The mantissa has an implicit 1 preceding the binary (radix) point. Assume that only 0\'s are padded in while shifting a field. The normalized representation of the above number (0.239 × 213) is:Question 42

Using a 4-bit 2’s complement arithmetic, which of the following additions will result in an overflow?

(i) 1100 + 1100

(ii) 0011 + 0111

(iii) 1111 + 0111

Question 44

Let X be the number of distinct 16-bit integers in 2’s complement representation. Let Y be the number of distinct 16-bit integers in sign magnitude representation. Then X −Y is _________

[This Question was originally a Fill-in-the-blanks Question]

Question 45

The addition of 4-bit, two\'s complement, binary numbers 1101 and 0100 results in

Question 46

The following bit pattern represents a floating point number in IEEE 754 single precision format

1 10000011 101000000000000000000000

The value of the number in decimal form is

Question 47

Question 49

The maximum gate delay for any output to appear in an array multiplier for multiplying two n bit number is:

Question 50

Zero has two representations in:

a) Sign magnitude

b) 1\'s complement

c) 2\'s complement

d) None of the above

There are 87 questions to complete.

Last Updated :

Take a part in the ongoing discussion