Logic functions and Minimization

Question 101

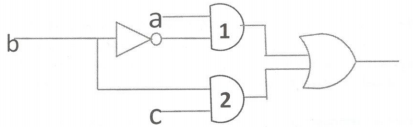

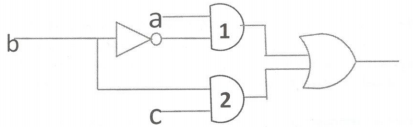

In the diagram above, the inverter (NOT gate) and the AND-gates labeled 1 and 2 have delays of 9, 10 and 12 nanoseconds(ns), respectively. Wire delays are negligible. For certain values of a and c, together with certain transition of b, a glitch (spurious output) is generated for a short time, after which the output assumes its correct value. The duration of the glitch is

Question 102

Any set of Boolean operators that is sufficient to represent all Boolean expressions is said to be complete. Which of the following is not complete?

Question 103

If a variable can take only integral values from 0 to n, where n is an integer, then the variable can be represented as a bit-field whose width is (the log in the answers are to the base 2, and [log n] means the floor of log n)

Question 104

Simplify the following using K-map :

F (A, B, C, D) = Σ (0, 1, 2, 8, 9, 12, 13)

d (A, B, C, D) = Σ (10, 11, 14, 15)

d stands for don’t care condition.

There are 104 questions to complete.

Last Updated :

Take a part in the ongoing discussion