GATE IT 2006

Question 71

An array X of n distinct integers is interpreted as a complete binary tree. The index of the first element of the array is 0. If only the root node does not satisfy the heap property, the algorithm to convert the complete binary tree into a heap has the best asymptotic time complexity of

Question 72

An array X of n distinct integers is interpreted as a complete binary tree. The index of the first element of the array is 0. If the root node is at level 0, the level of element X[i], i ≠ 0, is

Question 73

void swap(float* A1, float* A2)

{

float temp;

if (*A1 = = *A2) return;

temp = *A1;

*A1 = *A2;

*A2 = temp;

return;

}

Question 74

void swap(float* A1, float* A2)

{

float temp;

if (*A1 = = *A2) return;

temp = *A1;

*A1 = *A2;

*A2 = temp;

return;

}

Question 75

x + y/2 = 9

3x + y = 10

The value of the Frobenius norm for the above system of equations is:

Question 76

x + y/2 = 9

3x + y = 10

What can be said about the Gauss-Siedel iterative method for solving the above set of linear equations?

Question 77

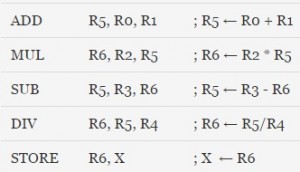

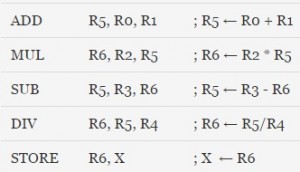

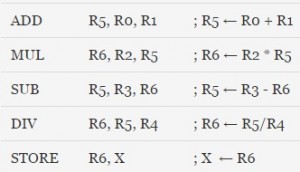

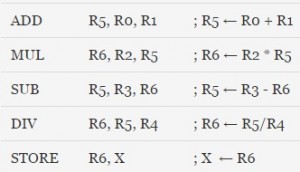

A pipelined processor uses a 4-stage instruction pipeline with the following stages: Instruction fetch (IF), Instruction decode (ID), Execute (EX) and Writeback (WB). The arithmetic operations as well as the load and store operations are carried out in the EX stage. The sequence of instructions corresponding to the statement X = (S - R * (P + Q))/T is given below. The values of variables P, Q, R, S and T are available in the registers R0, R1, R2, R3 and R4 respectively, before the execution of the instruction sequence.

The number of Read-After-Write (RAW) dependencies, Write-After-Read( WAR) dependencies, and Write-After-Write (WAW) dependencies in the sequence of instructions are, respectively,

The number of Read-After-Write (RAW) dependencies, Write-After-Read( WAR) dependencies, and Write-After-Write (WAW) dependencies in the sequence of instructions are, respectively,

Question 78

A pipelined processor uses a 4-stage instruction pipeline with the following stages: Instruction fetch (IF), Instruction decode (ID), Execute (EX) and Writeback (WB). The arithmetic operations as well as the load and store operations are carried out in the EX stage. The sequence of instructions corresponding to the statement X = (S - R * (P + Q))/T is given below. The values of variables P, Q, R, S and T are available in the registers R0, R1, R2, R3 and R4 respectively, before the execution of the instruction sequence.

The IF, ID and WB stages take 1 clock cycle each. The EX stage takes 1 clock cycle each for the ADD, SUB and STORE operations, and 3 clock cycles each for MUL and DIV operations. Operand forwarding from the EX stage to the ID stage is used. The number of clock cycles required to complete the sequence of instructions is

The IF, ID and WB stages take 1 clock cycle each. The EX stage takes 1 clock cycle each for the ADD, SUB and STORE operations, and 3 clock cycles each for MUL and DIV operations. Operand forwarding from the EX stage to the ID stage is used. The number of clock cycles required to complete the sequence of instructions is

The IF, ID and WB stages take 1 clock cycle each. The EX stage takes 1 clock cycle each for the ADD, SUB and STORE operations, and 3 clock cycles each for MUL and DIV operations. Operand forwarding from the EX stage to the ID stage is used. The number of clock cycles required to complete the sequence of instructions is

The IF, ID and WB stages take 1 clock cycle each. The EX stage takes 1 clock cycle each for the ADD, SUB and STORE operations, and 3 clock cycles each for MUL and DIV operations. Operand forwarding from the EX stage to the ID stage is used. The number of clock cycles required to complete the sequence of instructions isQuestion 79

Let L be a regular language. Consider the constructions on L below:

I. repeat (L) = {ww | w ∊ L}

II. prefix (L) = {u | ∃v : uv ∊ L}

III. suffix (L) = {v | ∃u : uv ∊ L}

IV. half (L) = {u | ∃v : | v | = | u | and uv ∊ L}

Which of the constructions could lead to a non-regular language?

I. repeat (L) = {ww | w ∊ L}

II. prefix (L) = {u | ∃v : uv ∊ L}

III. suffix (L) = {v | ∃u : uv ∊ L}

IV. half (L) = {u | ∃v : | v | = | u | and uv ∊ L}

Which of the constructions could lead to a non-regular language?

Question 80

Let L be a regular language. Consider the constructions on L below:

repeat (L) = {ww | w ∊ L}

prefix (L) = {u | ∃v : uv ∊ L}

suffix (L) = {v | ∃u uv ∊ L}

half (L) = {u | ∃v : | v | = | u | and uv ∊ L}

Which of the constructions could lead to a non-regular language?

There are 86 questions to complete.

Last Updated :

Take a part in the ongoing discussion