GATE-CS-2002

Question 26

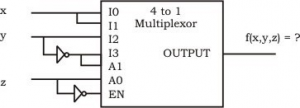

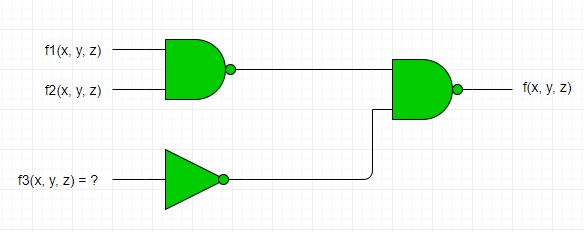

Consider the following logic circuit whose inputs and function and output is f.

Given that

Given that

Given that

Given that

f1(dx, y, z) = ∑(0, 1, 3, 5), f2(dx, y, z) = ∑(6, 7) and f(dx, y, z) = ∑(1, 4, 5),f3 is :

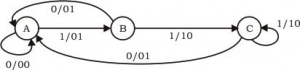

Question 27

Question 29

What are the states of the Auxiliary Carry (AC) and Carry Flag (dCY) after executing the following 8085 program?

MVI L, 5DH MVI L, 6BH MOV A, H ADD L

Question 30

There are 50 questions to complete.

Last Updated :

Take a part in the ongoing discussion