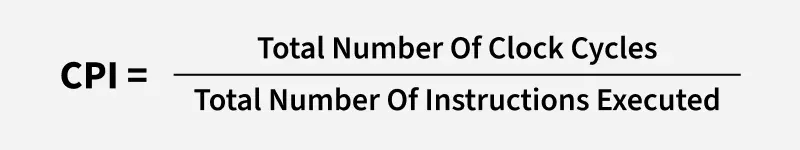

In Computer Architecture, Cycles Per Instruction (CPI) is a performance metric that indicates the average number of clock cycles a processor takes to execute one instruction. It reflects how efficiently the processor executes instructions based on its hardware design and instruction mix.

- Lower CPI means better processor performance.

- CPI links hardware efficiency with instruction execution.

- Techniques like pipelining and branch prediction help reduce CPI.

Basic Terms Related to CPI

Before diving deeper into CPI, let’s revise some basic concepts:

- Clock Cycle: The smallest unit of time in a processor. Each instruction takes one or more clock cycles to complete.

- Instruction: A single operation performed by the CPU (e.g., ADD, LOAD, STORE).

- Clock Rate (Frequency): The number of clock cycles per second, measured in Hz (commonly GHz).

Understanding CPI with Examples

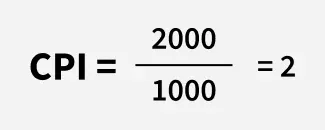

Example 1: Simple Case

Suppose a processor executes 1000 instructions in 2000 clock cycles.

Hence, on average, each instruction takes 2 cycles to execute.

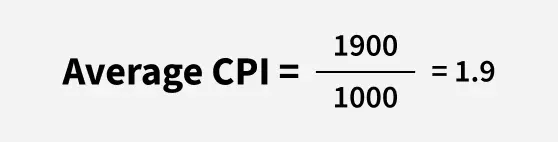

Example 2: Different Instruction Types

Not all instructions require the same number of cycles. Let’s consider:

| Instruction Type | Number of Instructions | Cycles per Instruction |

|---|---|---|

| Arithmetic | 400 | 1 |

| Load/Store | 300 | 2 |

| Branch | 300 | 3 |

Total cycles = (400×1) + (300×2) + (300×3) = 1900

Total instructions = 1000

So, the average CPI of this program is 1.9.

Example 3: Comparing Two CPUs

| Processor | Clock Rate | CPI | Instruction Count |

|---|---|---|---|

| A | 2 GHz | 2 | 1 million |

| B | 3 GHz | 3 | 1 million |

For Processor A:

CPU Time = (106 X 2) / (2 X 109) = 1 ms

For Processor B:

CPU Time = (106 X 3) / (3 X 109) = 1 ms

Note: Even though Processor B has a higher clock rate, its higher CPI results in the same total execution time.

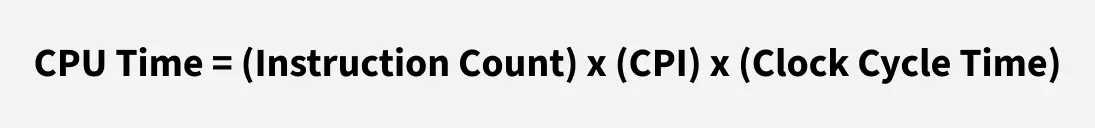

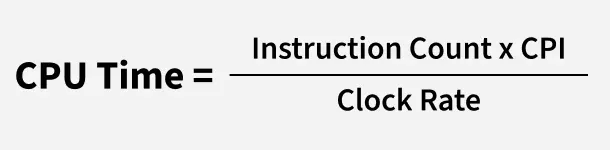

Relation Between CPI, Clock Rate, and CPU Time

The performance of a CPU can be expressed as:

or equivalently,

This formula helps compare how fast different processors execute the same program.

Factors Affecting CPI

Several factors influence the value of CPI:

- Instruction Mix: The proportion of different instruction types in a program (e.g., arithmetic, memory, branch).

- Processor Design: Pipelining allows overlapping of instructions, reducing CPI. Superscalar architecture executes multiple instructions per cycle, improving performance.

- Memory Hierarchy: Cache misses and slow memory access increase the number of cycles per instruction.

- Branch Prediction: Incorrect branch predictions can cause pipeline stalls, increasing CPI.

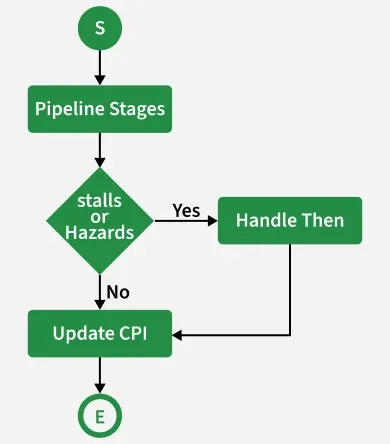

Ideal vs Real CPI

Ideal CPI

Ideal CPI is the minimum possible number of clock cycles per instruction that a processor could achieve under perfect conditions. This assumes:

- No pipeline stalls or hazards,

- Instantaneous memory access,

- Perfect branch prediction, and

- A fully optimized instruction flow.

For a fully pipelined processor, the ideal CPI is typically 1, meaning the processor can complete one instruction per clock cycle. Ideal CPI is a theoretical metric used to evaluate the best-case performance of a processor and to identify potential improvements in design or instruction scheduling.

Real CPI

Real CPI is the actual average number of clock cycles per instruction observed during program execution. It is usually greater than 1 because real processors face practical limitations such as:

- Memory delays (cache misses or slow main memory access),

- Pipeline hazards (data, control, or structural hazards), and

- Branch penalties (mis-predicted branches that cause pipeline flushes).

Real CPI reflects the true performance of a processor and helps in comparing different processor designs under real workloads. Designers often use the difference between ideal and real CPI to identify bottlenecks and optimize hardware or compiler strategies to improve performance.