Synchronous Data Transfer in Computer Organization

Last Updated :

20 Sep, 2023

In Synchronous Data Transfer, the sending and receiving units are enabled with the same clock signal. It is possible between two units when each of them knows the behaviour of the other. The master performs a sequence of instructions for data transfer in a predefined order. All these actions are synchronized with the common clock. The master is designed to supply the data at a time when the slave is definitely ready for it.

Usually, the master will introduce sufficient delay to take into account the slow response of the slave, without any request from the slave. The master does not expect any acknowledgement signal from the slave when data is sent by the master to the slave. Similarly, when data from the slave is read by the master, neither the slave informs that the data has been placed on the data bus nor the master acknowledges that the data has been read.

Both the master and slave perform their own task of transferring data at a designed clock period. Since both devices know the behaviour (response time) of each other, no difficulty arises. Prior to transferring data, the master must logically select the slave either by sending the slave’s address or sending a “device select” signal to the slave. But there is no acknowledgement signal from the slave to the master if the device is selected.

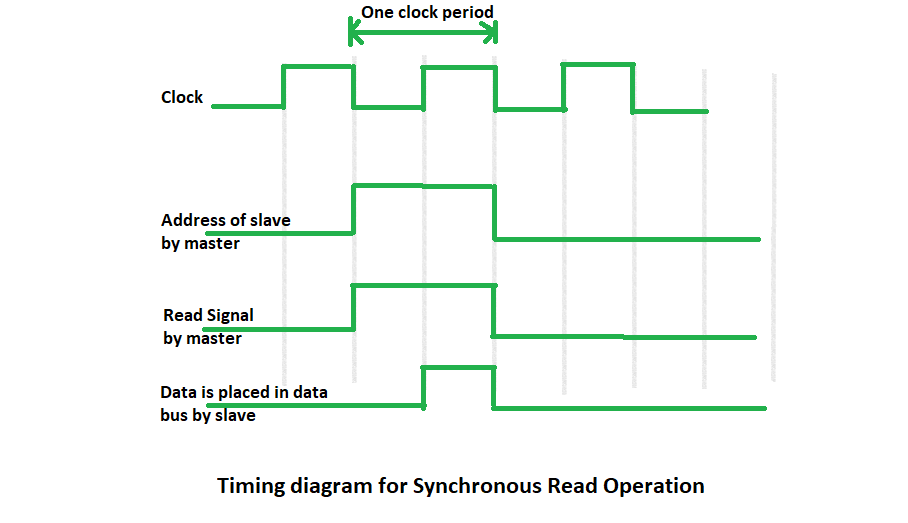

Timing Diagram for Synchronous Read Operation

In this timing diagram, the master first places the slave’s address in the address bus and read the signal in the control line at the falling edge of the clock. The entire read operation is over in one clock period.

Features of Synchronous Data Transfer

- Timing: In synchronous data transfer, the data transfer is synchronized with a common clock signal that is generated by the sending device and used by both the sending and receiving devices. This ensures that both devices are in sync and ready to receive or transmit data at the same time.

- Data Transfer Modes: Synchronous data transfer can be done using either the parallel or serial mode of data transfer. In parallel data transfer, multiple bits of data are transferred simultaneously, while in serial data transfer, data is transferred bit-by-bit using a single data line.

- Handshaking: Synchronous data transfer typically involves some form of handshaking between the sending and receiving devices to ensure that the data is transferred correctly. This can involve the use of signals such as Acknowledge (ACK) and Ready (RDY), which indicate that the receiving device is ready to receive or that the sending device has completed the transfer.

- Data Rate: The data transfer rate in synchronous data transfer is typically limited by the clock frequency and the number of bits that can be transferred in a single clock cycle. However, synchronous data transfer can be faster than asynchronous data transfer because there is no need to add extra bits for synchronization.

- Transmission Line: In synchronous data transfer, the transmission line used to transfer data must be properly designed and matched to the impedance of the devices to ensure that data is not lost due to reflections.

Advantages of Synchronous Data Transfer

- The design procedure is easy. The master does not wait for any acknowledgement signal from the slave, though the master waits for a time equal to the slave’s response time.

- The slave does not generate an acknowledge signal, though it obeys the timing rules as per the protocol set by the master or system designer.

Disadvantages of Synchronous Data Transfer

- If a slow-speed unit is connected to a common bus, it can degrade the overall rate of transfer in the system.

- If the slave operates at a slow speed, the master will be idle for some time during data transfer and vice versa.

FAQs on Synchronous Data Transfer

1. Can we use Synchronous Data Transfer for a long distance?

Answer:

Synchronous Data Transfer can be used over long distances. But we have to be careful while transferring data to a large distance because of signal degradation and timing issues.

2. Differentiate between Synchronous Data Transfer and Asynchronous Data Transfer?

Answer:

In synchronous Data Transfer, common clock signal is shared by both send and receiver that ensures trnafer of data at a specefic rate, whereas Asynchronous Data Transfer transfers data without a shared clock signal and it mostly rely on start and stop bits for synchronization purpose.

3. What is a ‘handshake’ in Synchronous Data Transfer?

Answer:

Handshake is a process that has the work of transferring signals for readiness and acknowledement during synchronous data transfer between sender and receiver.

4. How Data Sampling helps in Synchronous Data Transfer?

Answer:

Data Sampling helps in capturing data precisely at the intended time that corresponds to the clock signal.

5. What is Clock Signal in Synchronous Data Transfer?

Answer:

Clock Signal refers to the electrical pulse that serves as the timing reference for transmission of data.

Like Article

Suggest improvement

Share your thoughts in the comments

Please Login to comment...