Pipelined architecture with its diagram

Last Updated :

10 May, 2020

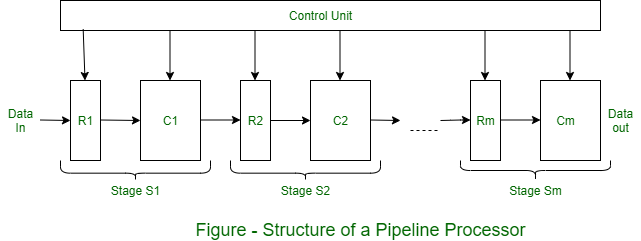

Pipeline Processor consists of a sequence of m data-processing circuits, called stages or segments, which collectively perform a single operation on a stream of data operands passing through them. Some processing takes place in each stage, but a final result is obtained only after an operand set has passed through the entire pipeline. As shown in figure, a stage S(i) contains a multiword input register or latch R(i), and a datapath circuit C(i), that is usually combinational. The R(i)‘s hold partially processed results as they move through the pipeline; they also serve as buffers that prevent neighbouring stages from interfering with one another.

A common clock signal causes the R(i)‘s to change state synchronously. Each R(i)‘s to change state synchronously. Each R(i) receives a new set of input data D(i-1) from the preceding stage S(i-1) except for R(1) whose data is supplied from an external source. D(i-1) represents the results computed by C(i-1) during the preceding clock period. Once D(i-1) has been loaded into R(i), C(i) proceeds to D(i-1) to computer a new data set D(i). Thus in each clock period, every stage transfers its previous results to the next stage and computers a new set of results.

Like Article

Suggest improvement

Share your thoughts in the comments

Please Login to comment...