ISRO CS 2014

Question 1

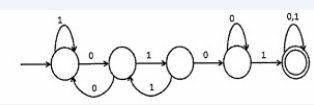

Consider the following Deterministic Finite Automaton.

Let denote the set of eight bit strings whose second, third, sixth and seventh bits are 1. The number of strings in that are accepted by M is

Let denote the set of eight bit strings whose second, third, sixth and seventh bits are 1. The number of strings in that are accepted by M is

Let denote the set of eight bit strings whose second, third, sixth and seventh bits are 1. The number of strings in that are accepted by M is

Let denote the set of eight bit strings whose second, third, sixth and seventh bits are 1. The number of strings in that are accepted by M isQuestion 2

Consider a 33 MHz CPU based system. What is the number of wait states required if it is interfaced with a 60 ns memory? Assume a maximum of 10 ns delay for additional circuitry like buffering and decoding.

Question 3

The number of states required by a Finite State Machine, to simulate the behavior of a computer with a memory capable of storing \'m\' words, each of length \'n\' bits is?

Question 4

What is the output of the following C program?

C

#include<stdio.h>

#define SQR(x) (x*x)

int main()

{

int a;

int b=4;

a=SQR(b+2);

printf(\"%d\\n\",a);

return 0;

}

Question 5

Consider the following pseudo code

while (m < n)

if (x > y ) and (a < b) then

a=a+1

y=y-1

end if

m=m+1

end while

What is cyclomatic complexity of the above pseudo code?

Question 6

What is the number of steps required to derive the string ((() ()) ())

S → SS S → (S) S → ε

Question 7

The process of modifying IP address information in IP packet headers while in transit across a traffic routing device is called

Question 9

In the standard IEEE 754 single precision floating point representation, there is 1 bit for sign, 23 bits for fraction and 8 bits for exponent. What is the precision in terms of the number of decimal digits?

Question 10

Let be the radius of the circle. What is the angle subtended by an arc of length at the center of the circle?

There are 80 questions to complete.

Last Updated :

Take a part in the ongoing discussion