Interview Preparation

- Interview Preparation For Software Developers

- Must Coding Questions - Company-wise

- Must Do Coding Questions - Topic-wise

- Company-wise Practice Problems

- Company Preparation

- Competitive Programming

- Software Design-Patterns

- Company-wise Interview Experience

- Experienced - Interview Experiences

- Internship - Interview Experiences

Commerce

- Commerce

- Class 11 Accountancy Notes

- Class 12 Accountancy Notes

- Accountancy

- Class 11 Business Studies Notes

- Class 12 Business Studies Notes

- Business Studies

- Class 11 Microeconomics Notes

- Class 11 Statistics For Economics Notes

- Class 12 Macroeconomics Notes

- Class 12 Indian Economic Development Notes

- Economics

- Management

- Income Tax

- Finance

GATE | GATE IT 2006 | Question 78

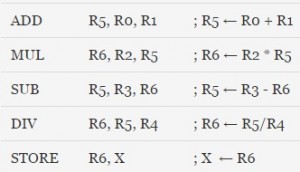

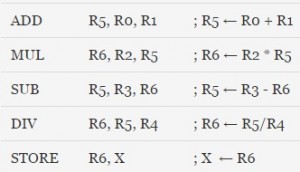

A pipelined processor uses a 4-stage instruction pipeline with the following stages: Instruction fetch (IF), Instruction decode (ID), Execute (EX) and Writeback (WB). The arithmetic operations as well as the load and store operations are carried out in the EX stage. The sequence of instructions corresponding to the statement X = (S - R * (P + Q))/T is given below. The values of variables P, Q, R, S and T are available in the registers R0, R1, R2, R3 and R4 respectively, before the execution of the instruction sequence.

The number of Read-After-Write (RAW) dependencies, Write-After-Read( WAR) dependencies, and Write-After-Write (WAW) dependencies in the sequence of instructions are, respectively,

The number of Read-After-Write (RAW) dependencies, Write-After-Read( WAR) dependencies, and Write-After-Write (WAW) dependencies in the sequence of instructions are, respectively,

(A)

2, 2, 4

(B)

3, 2, 3

(C)

4 ,2, 2

(D)

3 ,3, 2

Answer

Please comment below if you find anything wrong in the above post

Feeling lost in the world of random DSA topics, wasting time without progress? It's time for a change! Join our DSA course, where we'll guide you on an exciting journey to master DSA efficiently and on schedule.

Ready to dive in? Explore our Free Demo Content and join our DSA course, trusted by over 100,000 geeks!

Last Updated :

Share your thoughts in the comments

GeeksforGeeks