RISC and CISC in Computer Organization

Last Updated :

13 Mar, 2024

RISC is the way to make hardware simpler whereas CISC is the single instruction that handles multiple work. In this article, we are going to discuss RISC and CISC in detail as well as the Difference between RISC and CISC, Let’s proceed with RISC first.

Reduced Instruction Set Architecture (RISC)

The main idea behind this is to simplify hardware by using an instruction set composed of a few basic steps for loading, evaluating, and storing operations just like a load command will load data, a store command will store the data.

Characteristics of RISC

- Simpler instruction, hence simple instruction decoding.

- Instruction comes undersize of one word.

- Instruction takes a single clock cycle to get executed.

- More general-purpose registers.

- Simple Addressing Modes.

- Fewer Data types.

- A pipeline can be achieved.

Advantages of RISC

- Simpler instructions: RISC processors use a smaller set of simple instructions, which makes them easier to decode and execute quickly. This results in faster processing times.

- Faster execution: Because RISC processors have a simpler instruction set, they can execute instructions faster than CISC processors.

- Lower power consumption: RISC processors consume less power than CISC processors, making them ideal for portable devices.

Disadvantages of RISC

- More instructions required: RISC processors require more instructions to perform complex tasks than CISC processors.

- Increased memory usage: RISC processors require more memory to store the additional instructions needed to perform complex tasks.

- Higher cost: Developing and manufacturing RISC processors can be more expensive than CISC processors.

Complex Instruction Set Architecture (CISC)

The main idea is that a single instruction will do all loading, evaluating, and storing operations just like a multiplication command will do stuff like loading data, evaluating, and storing it, hence it’s complex.

Characteristics of CISC

- Complex instruction, hence complex instruction decoding.

- Instructions are larger than one-word size.

- Instruction may take more than a single clock cycle to get executed.

- Less number of general-purpose registers as operations get performed in memory itself.

- Complex Addressing Modes.

- More Data types.

Advantages of CISC

- Reduced code size: CISC processors use complex instructions that can perform multiple operations, reducing the amount of code needed to perform a task.

- More memory efficient: Because CISC instructions are more complex, they require fewer instructions to perform complex tasks, which can result in more memory-efficient code.

- Widely used: CISC processors have been in use for a longer time than RISC processors, so they have a larger user base and more available software.

Disadvantages of CISC

- Slower execution: CISC processors take longer to execute instructions because they have more complex instructions and need more time to decode them.

- More complex design: CISC processors have more complex instruction sets, which makes them more difficult to design and manufacture.

- Higher power consumption: CISC processors consume more power than RISC processors because of their more complex instruction sets.

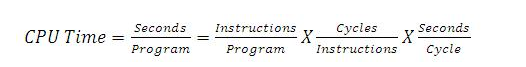

CPU Performance

Both approaches try to increase the CPU performance

- RISC: Reduce the cycles per instruction at the cost of the number of instructions per program.

CPU Time

- CISC: The CISC approach attempts to minimize the number of instructions per program but at the cost of an increase in the number of cycles per instruction.

Earlier when programming was done using assembly language, a need was felt to make instruction do more tasks because programming in assembly was tedious and error-prone due to which CISC architecture evolved but with the uprise of high-level language dependency on assembly reduced RISC architecture prevailed.

Example:

Suppose we have to add two 8-bit numbers:

- CISC approach: There will be a single command or instruction for this like ADD which will perform the task.

- RISC approach: Here programmer will write the first load command to load data in registers then it will use a suitable operator and then it will store the result in the desired location.

So, add operation is divided into parts i.e. load, operate, store due to which RISC programs are longer and require more memory to get stored but require fewer transistors due to less complex command.

RISC vs CISC

| RISC |

CISC |

| Focus on software |

Focus on hardware |

| Uses only Hardwired control unit |

Uses both hardwired and microprogrammed control unit |

| Transistors are used for more registers |

Transistors are used for storing complex

Instructions |

| Fixed sized instructions |

Variable sized instructions |

| Can perform only Register to Register Arithmetic operations |

Can perform REG to REG or REG to MEM or MEM to MEM |

| Requires more number of registers |

Requires less number of registers |

| Code size is large |

Code size is small |

| An instruction executed in a single clock cycle |

Instruction takes more than one clock cycle |

| An instruction fit in one word. |

Instructions are larger than the size of one word |

| Simple and limited addressing modes. |

Complex and more addressing modes. |

| RISC is Reduced Instruction Cycle. |

CISC is Complex Instruction Cycle. |

| The number of instructions are less as compared to CISC. |

The number of instructions are more as compared to RISC. |

| It consumes the low power. |

It consumes more/high power. |

| RISC is highly pipelined. |

CISC is less pipelined. |

| RISC required more RAM. |

CISC required less RAM. |

| Here, Addressing modes are less. |

Here, Addressing modes are more. |

FAQs on RISC and CISC

Q. 1: Does RISC architectures simple or complex?

Answer:

RISC Architectures are simple in individual instruction that aims for faster execution and efficient pipelining.

Q. 2: How memory is accessed in CISC?

Answer:

Memory is accessed in CISC by allowing direct memory-to-memory operations that helps in reducing the need for explicit register handling.

Like Article

Suggest improvement

Share your thoughts in the comments

Please Login to comment...