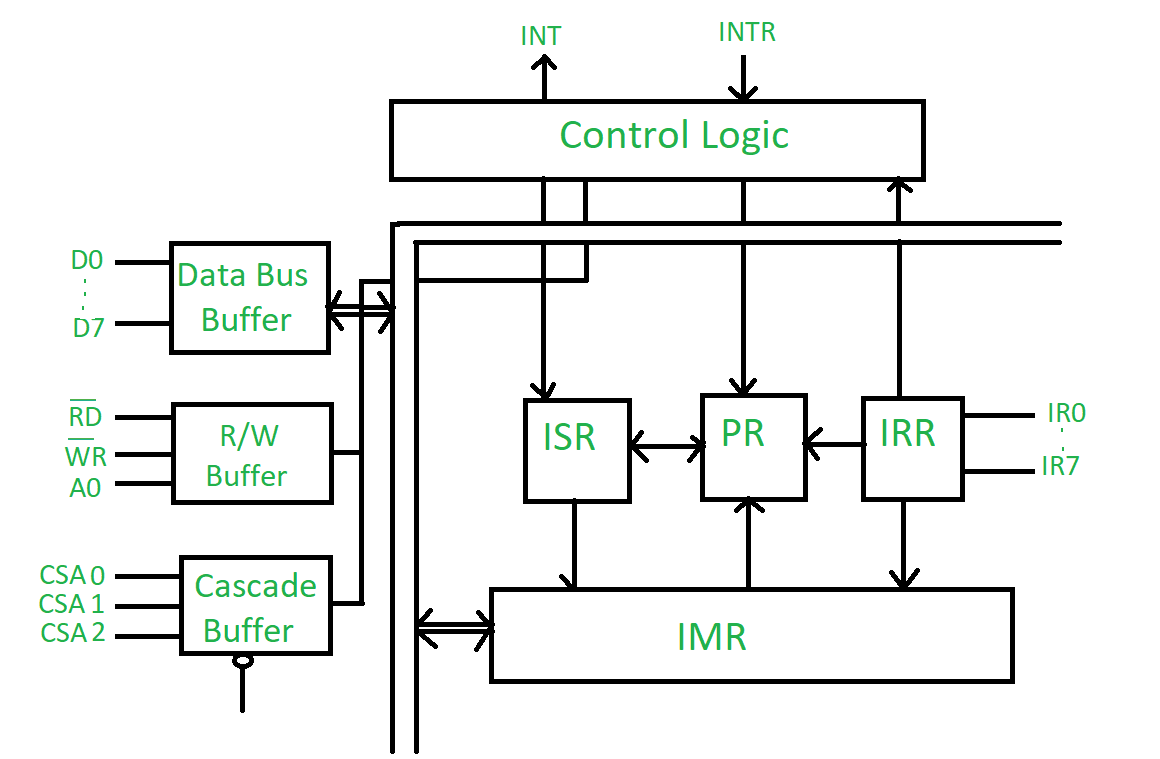

Block Diagram of 8259 Microprocessor

Last Updated :

14 May, 2023

- 8259 microprocessor can be programmed according to given interrupts condition and it can be provided either with level or edge-triggered interrupt level.

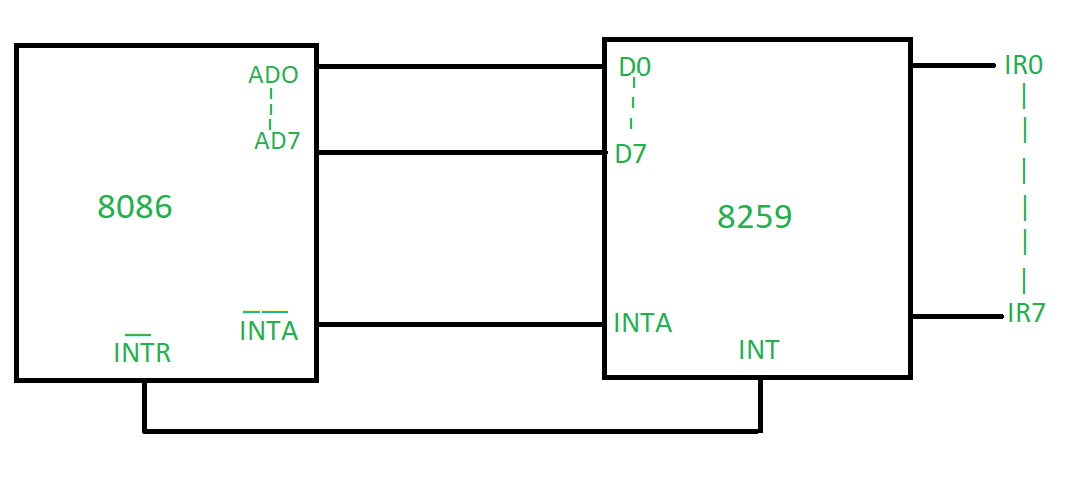

- It can be programmed to either work in 8085 or in 8086 microprocessors.

- Individual interrupt bits can be masked.

- By cascading Nine 8259’s in Master-Slave Configuration we can handle up to 64 interrupt pins.

It contains 3 registers commonly known as ISR, IRR, IMR & there is 1 priority resolver (PR).

- Interrupt Request Register (IRR): It stores those bits which are requested for their interrupt services.

- Interrupt Service Register (ISR): It stores the interrupt levels which is currently being served.

- Interrupt Mask Register (IMR): It stores interrupt levels that have to be masked. These interrupt levels are already accepted by the 8259 microprocessor.

Priority Resolver (PR): It examines all the 3 registers and sets the priority of interrupts and sets the interrupt levels in ISR which has the highest priority and the rest of the interrupt bit is IRR which is already accepted.

SP/EN (low active pin): If its value is 1 it works in master mode & if its value=e is 0 then it works in slave mode.

Cascade Buffer: It is used to cascade more number of Programmable Interrupt Controller to increase the interrupts handling capability up to 64 levels.

Advantages:

Interrupt management: The 8259 microprocessor is a specialized chip that is dedicated to managing interrupts, which can help to improve system performance and reduce the workload on the main CPU.

Programmability: The 8259 microprocessor is programmable, which means that it can be customized to handle specific types of interrupts and to prioritize different interrupt requests.

Compatibility: The 8259 microprocessor is compatible with a wide range of microprocessors, making it a popular choice for interrupt management in many different systems.

Multiple interrupt inputs: The 8259 microprocessor can handle multiple interrupt inputs, which makes it a useful peripheral for managing complex systems with multiple devices.

Ease of use: The 8259 microprocessor includes simple interface pins and registers, making it relatively easy to use and program.

Disadvantages:

Cost: While the 8259 microprocessor is relatively affordable, it does add cost to a system, particularly if multiple 8259s are required.

Limited functionality: While the 8259 microprocessor is a useful peripheral for interrupt management, it does not include more advanced features, such as DMA (direct memory access) or advanced error correction.

Limited number of interrupts: The 8259 microprocessor can only handle a limited number of interrupt requests at once, which may be insufficient for some applications.

Complex programming: Although the interface pins and registers of the 8259 microprocessor are relatively simple, programming the 8259 can be complex, requiring careful attention to interrupt prioritization and other parameters.

Like Article

Suggest improvement

Share your thoughts in the comments

Please Login to comment...